Features & Benefits

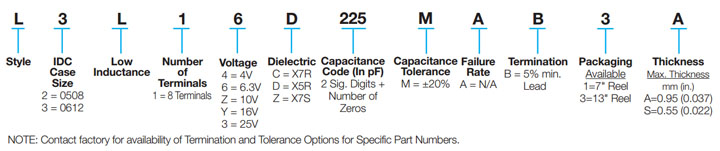

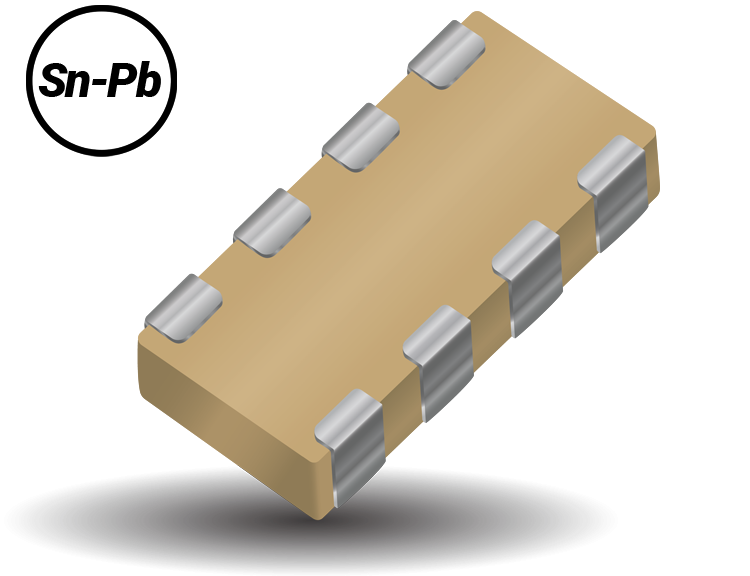

- 0306, 0508, 0612 sizes utilizing X7R, X7S or X5R dielectrics with options to have up to 8 terminals

- Voltage Ratings: 4, 6.3, 10, 16, 25V

- Capacitance Range: 0.01µF (min) – 3.3µF (max)

Typical Applications

- Semiconductor package

- Board level decoupling

- Typically used on packages of semiconductor products with power levels of 15 watts or greater

- Used on CPU, GPU, ASIC, and ASSP devices produced on 0.13μ, 90nm, 65nm, and 45nm processes

- Used on both ceramic and organic package substrates

The size of a current loop has the greatest impact on the ESL characteristics of a surface mount capacitor. There is a secondary method for decreasing the ESL of a capacitor. This secondary method uses adjacent opposing current loops to reduce ESL. The InterDigitated Capacitor (IDC) utilizes both primary and secondary methods of reducing inductance. The IDC architecture shrinks the distance between terminations to minimize the current loop size, then further reduces inductance by creating adjacent opposing current loops.

An IDC is one single capacitor with an internal structure that has been optimized for low ESL. Similar to standard MLCC versus LICCs, the reduction in ESL varies by EIA case size. Typically, for the same EIA size, an IDC delivers an ESL that is at least 80% lower than an MLCC.