Kyocera Begins Mass Production of Differential Clock Crystal Oscillators

Delivering Industry-Leading*1 30 fs Phase Jitter

Enabling Low Noise, Low Power Solutions for AI Server Data Communication

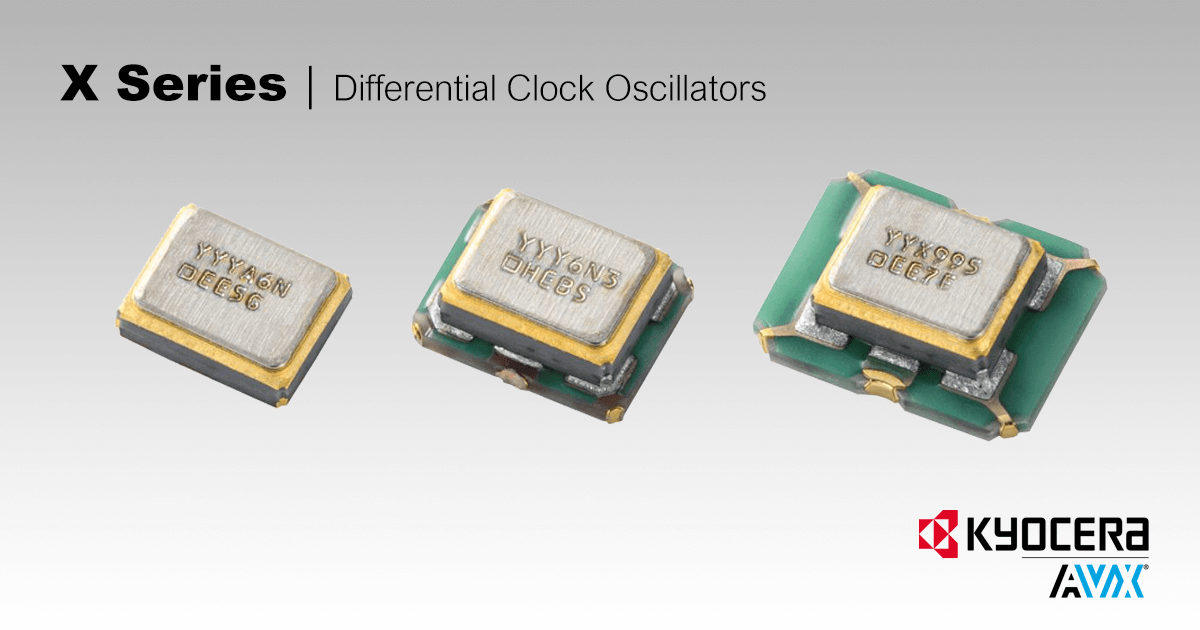

Kyocera Corporation (President: Hideo Tanimoto) today announced the launch and commencement of mass production in January 2026 of its “X Series” of differential clock crystal oscillators, achieving industry-leading low phase jitter of 30fs (femtoseconds) and low noise. Mass production commenced in January 2026.

Differential clock crystal oscillators play an important role in enabling high-speed, large-capacity data communication in areas such as AI servers, offering enhanced noise resistance compared to standard clock crystal oscillators.

Kyocera began mass production of the “X Series” in January this year with an initial monthly output of 200,000 units. In response to growing demand created by the widespread adoption of generative AI and the ongoing expansion of the AI server market, the company plans to increase production capacity to 2 million units per month from June. This strategic initiative will enable Kyocera to effectively address the evolving needs of this rapidly expanding sector.

■ Background of Development

While clock crystal oscillators utilized in standard electronic devices, such as smartphones, generally offer a single-ended output, differential clock oscillators generate two signals. By evaluating the difference between these signals at the receiving end, differential oscillators offer strong noise resistance and enable stable signal transmission, making them ideal for high-speed, long-distance communication.

In light of the expanding 5G network infrastructure and the increasing prevalence of AI data centers, there has been a notable surge in demand for enhanced data communication capabilities in network equipment and servers. In high-speed communication, noise and timing misalignment can result in bit errors. Consequently, there is an increasing demand for highly precise differential clock crystal oscillators with “low phase jitter characteristics,” meaning extremely small timing deviations in the signal.

The “X Series,” newly commercialized by Kyocera, is a differential clock crystal oscillator that achieves industry-leading*1 low noise with a phase jitter of 30 fs.

■ Key Features

1. Achieves Industry-Leading 30 fs Low Phase Jitter

Achieving a 30fs phase jitter required a blend of high-quality crystals and advanced ICs. The Kyocera X Series has achieved this industry-leading level through the integration of proprietary semiconductor photolithography, a compact design approach with the plasma CVM fabrication method, and high-performance ICs. Compared to conventional products running at the same frequency, the X Series reduces phase jitter by about 25%, thereby significantly reducing errors in high-speed communication.

2. Significantly Reduced Power Consumption by Approximately 42% Compared to Conventional Products

By incorporating a new differential-output oscillator IC, Kyocera has greatly reduced power consumption, enabling notable energy savings in AI servers and other high-performance computing equipment. For the 156.25 MHz (LV-PECL output) configuration, the X Series consumes 29 mA, a 42% reduction compared to the 50mA typical of conventional products.

■ Main Applications

- AI Servers

- Optical Transceivers

- Storage Applications

- Automotive ADAS Equipment

■ X Series Differential Clock Crystal Oscillators: Product Overview

| Package Size (mm, MAX.) | 2.0 × 1.6 × 0.5 mm 2.5 × 2.0 × 0.5 mm 3.2 × 2.5 × 0.5 mm |

| Production Site | Higashine Plant, Yamagata, Japan |

| Operating Temperature Range | –40 to +85°C –40 to +105°C |

| Output Frequency Range | 100 MHz / 125 MHz / 156.25 MHz / 312.5 MHz |

| Output Type | LV-PECL / LVDS |

| Frequency Tolerance*2 | ±15 ppm (–40 to +85°C) ±20 ppm (–40 to +105°C) |

| Supply Voltage | 1.8 V / 2.5 V / 3.3 V (1.8 V available for LVDS output only) |

| Current Consumption Phase Jitter (Typical) | 29 mA (LV-PECL output) / 156.25 MHz 14 mA (LVDS output) / 156.25 MHz 45 mA (LV-PECL output) / 312.5 MHz 23 mA (LVDS output) / 312.5 MHz |

| Jitter (Typical) | 40 fs / 156.25 MHz 30 fs / 312.5 MHz |

-

*2

- Initial Frequency Tolerance @ 25°C

- Frequency Stability over Operating Temperature

- Frequency Stability vs. Power Supply Voltage Variation

- Frequency Stability vs. Load Capacitance Variation

- Frequency Aging (1st year @ 25°C)

- Resistance to Vibration and Shock

■ For More Information

For more information please visit Kyocera’s product introduction page!

Learn More Glossary- Phase Jitter: A deviation in the signal timing of clock crystal oscillators.

- 30fs: A unit of time (femtosecond) representing the signal timing of a crystal oscillator, where one femtosecond is 10-15 seconds (one quadrillionth of a second).

- Bit Error: An error in data that occurs during data transmission or storage.

References

- X Series Details: Kyocera Website URL: https://ele.kyocera.com/en/technical/xtal_npikcx/

- Plasma CVM Fabrication Method: URL: https://youtu.be/cfs6DjD_gP0